AITIA's 1 Gb/s high throughput TCP sender core

We developed this core to ensure lossless transfer of processed frames between the FPGA and the receiving monitor PC-s. Therefore the main goal was to create a hardware optimized implementation to maximize performance and liability.

Features:

- RFC 675/RFC 793 compliant implementation

- Source code available for further development!

- Fabric side interface is configurable for different 1G MAC modules

- User side interface is configurable for different applications (64 bit@125MHz by default)

- 8/16/32/64 Kbyte selectable internal buffer for retransmissions

- basic ARP protocol implementation (request,response)

- implements modified slow start, and keep alive sending

- implements hardware optimized fast retransmit, and conguestion avoidance algorithms

- tested on CBOARD/C-GEP 20 with SFP modules, and IBM compatible PC-s running Windos and Linux systems

- Sample application available

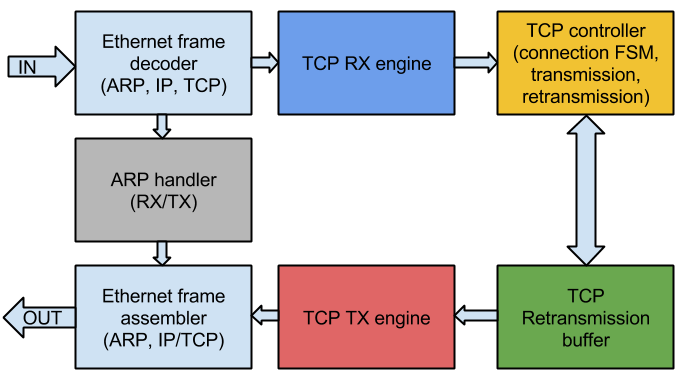

TCP Sender core block diagram